We came across something concerning this system in Verilog. This blog will go over the system Verilog loop statement.

It may come into circumstances where a piece of code has to be performed several times. In general, statements are executed in the following order: the first statement in a function is executed first, then the second, and so on.

Control structures in programming languages allow for more sophisticated execution routes.

A loop statement allows us to repeat a sentence or a combination of statements. The general form of a loop statement in most programming languages is shown below.

C/C++ looping statements are all too familiar to us. SystemVerilog has six distinct looping constructs:

- for

- while

- do-while

- foreach

- forever

- repeat

Let us look at each with more explanation.

for Loop

Here’s a basic example that explains everything:

module forloop;

int i;

int mem[0:3];

initial begin

//variable within the loop

outerLoop: for (int j = 0; j < 2; j++) begin

#10;

//variable outside the loop

innerLoop: for (i = 0; i < 3; i++) begin

mem[i] = i+1;

$display($stime,,, "mem[%0d] = %0d",i, mem[i]);

end

end

end

endmodule

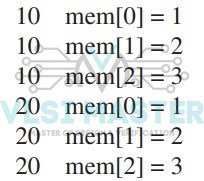

Figure 1 shows the output of the above example of the “for” loop.

Fig 1: For Loop Example

The variable used to control the for loop, In our case, “i” can be defined before the loop.

However, if loops in two or more parallel processes utilize the same loop control variable, there is a risk that one loop will overwrite the value while the other is still executing on it.

The variable used to control the for loop, on the other hand, can be declared within the loop itself, In our example, “j”.

This wraps the loop in an implicit begin-end block. An implicit begin-end block establishes a new hierarchical scope, causing the variables to become local to the loop scope.

repeat Loop

The repeat loop performs a statement a certain number of times (repeat expression).

Here’s an example of a repeat loop:

module forloop; int i; int mem[0:7]; bit clk; parameter repeatNum = 3; initial begin outerLoop: for (int j = 0; j < 2; j++) begin innerLoop: repeat (repeatNum) //REPEAT LOOP begin @(posedge clk); i++; storeMem ( i ); //task call $display($stime,,, "mem[%0d] = %0d",i, mem[i]); end end end task storeMem ( int i ); begin mem[i] = i + 1; end endtask initial begin clk = 0; #120 $finish(2); end always #10 clk = !clk; endmodule

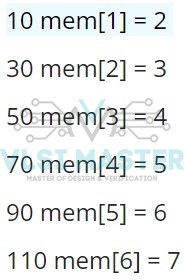

Figure 2 shows the output of the above example of the “repeat” loop.

Fig 2: Repeat Loop Output

In this example, we can see a combination of a for loop and a repeat loop.

The repeat loop (“innerLoop”) repeats itself “repeatNum” times (the parameter “repeatNum”).

“repeatNum” times, the complete begin-end block will be run.

Waiting for @(posedge clk) within this begin-end and then running a task “storeMem” to store the value of “i” in the memory “mem.” The purpose of this code is to demonstrate that sophisticated code may be contained within a repeat loop.

It is important to note that if the repeat expression is “x” or “z,” the repeat count is regarded as zero, and no statements associated with “repeat” are performed.

foreach Loop

The foreach loop component specifies looping across array items. Its parameter is an identifier that can be any type of array surrounded by square brackets. Each loop variable corresponds to one of the array’s dimensions.

module for_loop;

int a[4];

initial begin

$display("-----------------------------------------------------------------");

foreach(a[i]) a[i] = i;

foreach(a[i]) $display("\tValue of a[%0d]=%0d",i,a[i]);

$display("-----------------------------------------------------------------");

end

endmodule

Figure 3 shows the output of the above example of the “foreach” loop.

Fig 3: Foreach Loop Example

while Loop

The while loop runs a sentence continuously as long as a control expression is true. Here’s an illustration:

module tb; logic [2:0] count; logic [3:0] mem[0:7]; initial begin count = 4; while (count) begin mem[count] = $urandom; $display($stime,,, "mem[%0d] = %0h", count, mem[count]); count--; end end endmodule

In this case, the control phrase is “count.” The loop will run as long as “count” is true. We begin with “count = 4” and decrease it with each iteration.

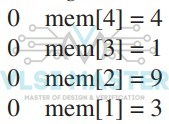

As a result, the loop will run four times, as indicated in Figure 4.

Fig 4: While Loop Example

do – while Loop

The do-while loop is distinct from the while loop in that it tests its control expression at the conclusion of the loop.

We will see in the below example that we just altered the prior example to check for the control expression at the conclusion of the loop+.

module tb; logic [2:0] count; logic [3:0] mem[0:7]; initial begin count = 4; do begin mem[count] = $urandom; $display($stime,,, "mem[%0d] = %0h",count,mem[count]); count--; end while (count); end

The loop is initiated with the command “do begin.” It decrements “count” with each loop iteration.

Output is the same as shown in Figure 4.

forever Loop

The “forever” loop, as the name implies, runs a statement indefinitely.

This is an infinite loop, it must include some type of timing control; otherwise, it will end up in a 0-delay loop, causing simulation to hang.

It can’t have an “always” block within the “initial” block, the “forever” loop is most beneficial in the “initial” block.

Let’s see a clock generator example for more clarification.

module tb; bit clk; bit [7:0] count; initial begin clk = 0; forever begin #10 clk = !clk; $display ($stime,,,"clk = %0d",clk); end end initial begin #60; $finish(2); end endmodule

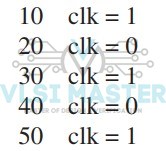

Figure 5 shows the output of the above example of the “forever” loop.

Fig 5: Forever Loop Example

To produce a clock, we establish a “forever” loop within the “beginning” block.

This “forever” will run till the simulation is completed.

Now we will see a jump statement function in System Verilog.

Jump Statements

Jump statements execute an unconditional jump to another statement in the code. They are mostly used to break switch statements and loops.

The jump statements are the go to statement, continue statement, break statement, and return statement.

“break” and “continue”

“break” exits a loop, whereas “continue” advances to the conclusion of the loop. These controls are identical to those found in the “C” programming language.

Here’s an example of breaking out of a loop:

module tb; logic [2:0] count; logic [3:0] mem[0:7]; initial begin count = 4; while (count) begin #10; mem[count] = $urandom; $display($stime,,, "mem[%0d] = %0h",count,mem[count]); count--; break; end $display($stime,,, "After 'while' loop"); end initial #60 $finish(2); endmodule

This example is similar to the last one on while loops. However, after the first iteration, we exit the loop.

As a result, “mem[count] = $urandom” will only be run once (as evident from the simulation log). When the “break” out of the loop, the control moves to the statement that follows the loop block.

Output is shown in Figure 6.

Fig 6: Break and Continue Example

We saw the loop and jump commands in System Verilog from this blog and understood them with an appropriate example.

So let’s summarise the entire blog by asking a few key questions about it.

- What exactly is a loop statement?

- How many distinct types of loop statements exist?

- What is the difference between a while loop and a do-while loop?

- What is the purpose of an “forever” loop?

- What exactly is a “jump statement”?

- What is the purpose of a break and continue statement, as illustrated by an example?