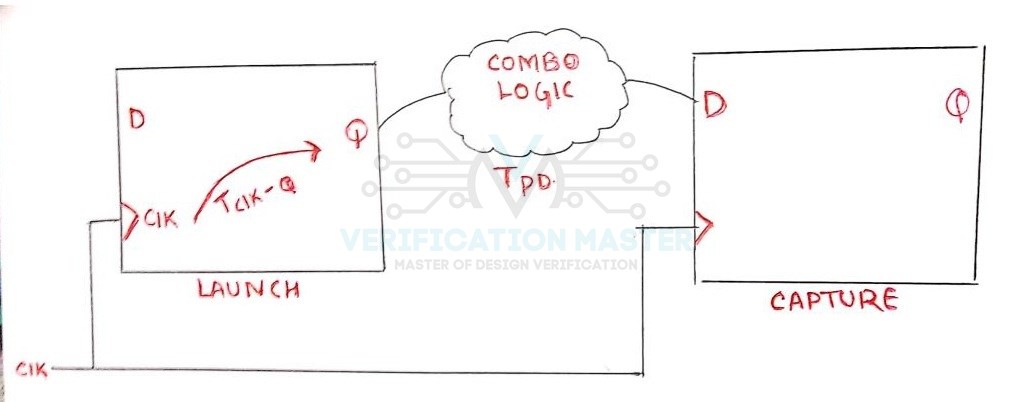

There are Setup and Hold checks in a design that ensures the data launched from the Launch Flop is captured correctly at the Capture Flop. The data launched at the Current Active Edge of the clock should be captured at the next Active Edge of the Clock. For this, the data should arrive at Setup Time before the next Active Edge and should remain stable for Hold Time after the Current Active Edge. So to ensure this the Data Launched from the Launching Flop should only arrive at the input pin of the next Flop after completing the Hold Time so that Data Signal is captured correctly (for hold check). Remember that Setup is checked at the next active edge and Hold is checked at the current active edge. Also, the delay between Launch Flop and Capture Flop should not be greater than the “Time Period – Setup Requirement of Capture Flop”.

So Mathematically it can be expressed as

Setup

T(clk-q) + T(propagation delay) + T(setup) < T(period)

Hold

T(clk-q) + T(propagation delay) > T(hold)

Where T(clk-q) is Clock to Q Delay of Launch Flip-Flop, T(propagation delay) is the delay of the Combo Logic.

Fig. 1: Time Period -Setup Requirement of Capture Flop

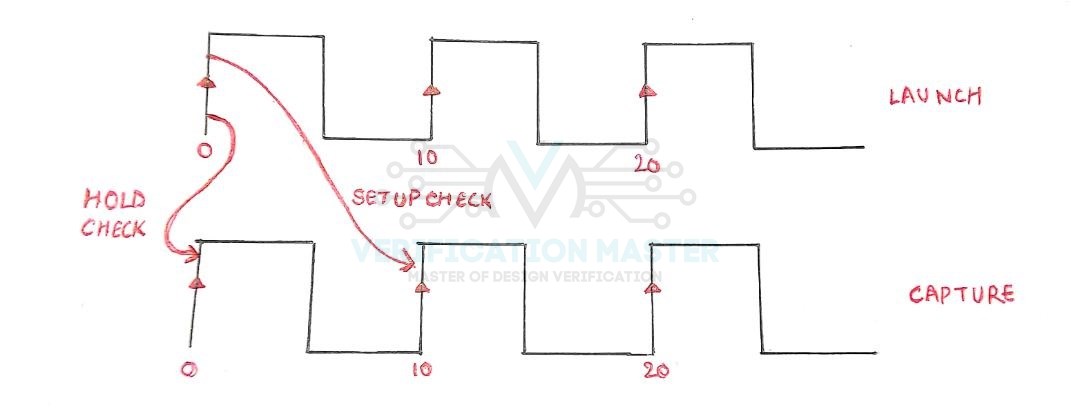

Fig. 2: Setup Check and Hold Check

So, the above two equations are mathematical equations for Setup and Hold check respectively. From Fig.2 we can see Data Launched at 0ns should reach before 10 ns at the Capture Flop to be Captured correctly and satisfy Setup requirements. Similarly, Data Launched at 0ns should be stable for some time after the active edge to satisfy Hold Requirements. Hold check is independent of the Time Period and this is the reason why hold check is more critical than the setup check. Once the Chip is fabricated and there is an accidental Setup violation it can be improved by lowering the Frequency but if there is a Hold violation after fabrication then the Chip is of no use.

Setup Slack and Hold Slack

Slack is a parameter that tells if there is any setup or holds violations. If slack is +ve then there is no violation and if slack is -ve then there is a violation and it should be fixed.

Setup Slack

T(period) – [T(clk-q) + T(propagation delay) + T(setup)]

Hold Slack

T(clk-q) + T(propagation delay) – T(hold)

Why Setup is Checked for worst case and Hold is checked for best case ?

Data Path Delay

Delay introduced in a path traversed by Data Signal from its start point to an endpoint is known as Data Path Delay.

Clock Path Delay

Delay introduced in a path traversed by a Clock Signal from its Source Point to its Sink Point is known as Clock Path Delay.

Worst Case

Maximum data path delay and minimum clock path delay.

Best Case

Minimum data path delay and maximum clock path delay.

For Setup worst case is that how late Data can arrive and how early a Clock can arrive. If the Setup Check is made Violation-free in this case then automatically it will satisfy the other conditions also.

To Hold, the best case is that how early Data can arrive and how late a Clock can arrive. If the Hold check is made Violation-free in this case, then automatically it will satisfy the other conditions also.

So, from this blog you can now answer the below questions

- Q1) What is setup check and hold check?

- Q2) Give equations for setup check and hold check.

- Q3) What is more critical ? Setup check or Hold check and Why?

- Q4) What is Slack and different types of Slack?

- Q5) Why is Setup checked for worst case and Hold is checked for best case ?