Basic Concept

In this blog, we will go through the fundamental structures and practices of Verilog. These conventions and constructions are utilised in the following blog. These conventions form the foundation for Verilog HDL. Data types closely resemble actual data storage and switch components in hardware.

This blog may appear dense, yet grasping these ideas is essential for the upcoming blogs. So let’s start this blog with more zeal. At first, we will try to understand the lexical conventions used in Verilog HDL.

Lexical Conventions

The Verilog HDL’s core lexical conventions are comparable to those of the C programming language.

A programme is made up of a series of tokens. Comments, delimiters, integers, strings, identifiers, and keywords are all examples of tokens. Verilog HDL is a case-sensitive programming language. All keywords are written in lowercase.

Different types of lexical conventions are as follows:

Whitespace

Whitespace is made up of blank spaces (b), tabs (t), and newlines (n). Except when it separates tokens, whitespace is disregarded by Verilog. Strings do not disregard whitespace.

Comments

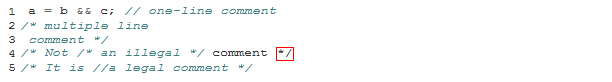

For readability and documentation, comments can be added to the code. There are two methods for leaving comments.

- The first line of a one-line remark is “//”. After that from that point, Verilog jumps to the end of the line.

- A multi-line comment begins with “/*” and concludes with “/*”.

Nesting multiple-line comments is not possible. One-line comments, on the other hand, can be incorporated into multiple-line comments.

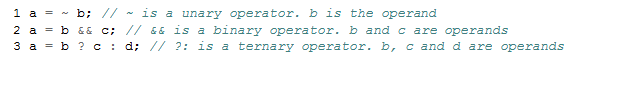

Operators

There are three sorts of operators: unary, binary, and ternary. The operand is preceded by unary operators. Between two operands, binary operators occur. Ternary operators consist of two distinct operators that split three operands.

Number Specifications

In Verilog, there are two sorts of number specifications: sized and unsized.

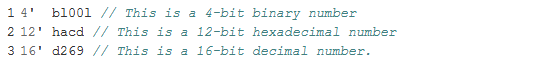

- Sized numbers

Sized numbers are represented as <size> ‘<base format> <number>.

<size> defines the amount of bits in the number and is only written in decimal. Decimal (‘d or ‘D), hexadecimal (‘h or ‘H), binary (‘b or ‘B), and octal (‘o or ‘O) are legal base formats.

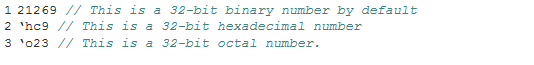

- Unsized numbers

These numbers do not have a base format specification, i.e., are decimal numbers by default, and are not with a base format specification.

Strings

A string is a series of characters separated by double quotes. A string is restricted to being contained on a single line, that is, without a carriage return. It cannot be on more than one line. Strings are considered to be a series of one-byte ASCII values.

Identifiers and Keywords

Keywords are unique identifiers used to specify language constructs. Lowercase is used for keywords.

Identifiers are names assigned to things in order for them to be referenced in the design. They are case-sensitive and consist of alphanumeric characters, the underscore (_), and the dollar symbol ($).

![]()

Escaped Identifiers

Escaped identifiers start with a backslash (/) and terminate with whitespace (space, tab, or newline).

Data Types

This section goes through the data types that are utilised in Verilog.

Value Levels

To represent the functioning of real hardware, verilog allows four values and eight strengths.

| Value Level | Condition in Hardware Circuits |

| 0 | Logic Zero, false condition |

| 1 | Logic one, true condition |

| X | Unknown Value |

| Z | High Impedance, Floating State |

Table 1: Value Levels

Strength levels, in addition to logic values, are frequently utilised in digital circuits to resolve conflicts between drivers of varying strengths. The strength levels mentioned in Table 2 can be assigned to value levels 0 and 1.

| Strength Level | Type | Degree |

| Supply | Driving | strongest |

| Strong | Driving | . |

| Pull | Driving | . |

| Large | Storage | . |

| Weak | Driving | . |

| Medium | Storage | . |

| Small | Storage | . |

| highz | High Impedance | Weakest |

Table 2: Strength Level

When two signals of unequal strength are sent down a wire, the stronger signal wins.

Nets

Nets represent the interconnection of hardware pieces. Nets, like actual circuits, have values constantly pushed on them by the outputs of devices to which they are linked.

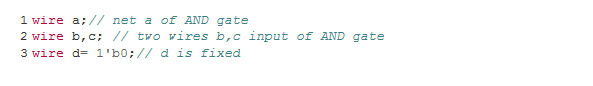

Fig1: Nets Example

In Figure 1 output of AND gate is net a and it will always get the value of AND gate as the input provided in b and c.

Registers

Registers are data-storing components. Registers keep their value until another value is assigned to them.

The word “registers” in Verilog should not be confused with hardware registers formed from edge-triggered flip-flops in actual circuits. In Verilog, a register is just a variable that may contain a value.

| 1 |

reg reset: // declare a reset

|

Vectors

Nets of register data both can be stated as vectors. It can be declared at [high#: low#] or [low#: high#].

Integer, Real, and Time Register Data type

These are also supported in Verilog.

The term “int” declares an integer, which is a general-purpose register data type used for manipulating quantities.

The keyword real is used to specify real number constants and the real register data type.

Verilog simulation is performed with simulation time in mind, and a particular one is used in Verilog to record simulation time.

Arrays

Verilog supports arrays for the reg, integer, time, and vector register data types. Arrays are not permitted for real variables. Arrays are accessed using <array_name>[<subscript>]. Verilog does not allow multidimensional arrays.

Memories

In digital simulation, register files, RAMs, and ROMs are frequently modelled. In Verilog, memories are simply represented as an array of registers. Each array element is referred to as a word. Each word can consist of one or more bits. It is critical to distinguish between n-bit registers and one n-bit register. The address is used as a memory array subscript to locate a specific word in memory.

![]()

Parameters

The keyword parameter in Verilog allows constants to be declared in a module. Variables cannot be used with parameters. At compilation time, parameter values for each module instance can be altered independently.

Strings

Strings can be kept in reg. The width of the register variables must be sufficient to accommodate the string. Each character in the string consumes eight bits (1 byte). Verilog fills the bits to the left of the string with zeros if the width of the register is higher than the size of the string.

And we learned the fundamentals of Verilog with the help of this blog. So let’s summarise the whole blog with some questions for more clarification.

- What are the basic concepts of Verilog?

- What is a lexical convention?

- What are the types of lexical conventions?

- What are Data types?

- What do you mean by Nets?

- What do you mean by registers and how is it different from hardware registers?

- What are Verilog Memories?