We have studied the different types of assignments in our previous blog in which we studied the different types of modelling and explained each term briefly. Today we will study the blog related to it.

Delay values govern the period between when a right-hand operand changes and when the new value is allocated to the left-hand side. Regular assignment delay, implicit continuous assignment delay, and net declaration delay are three techniques to define delays in continuous assignment statements.

Assignment Delay

The first option is to use a continuous assignment statement to assign a delay value. After the keyword is assigned, the delay value is supplied.

Any change in the values of input a or b will cause a delay of 10 time units before the expressions input a and b are recalculated, and the result will be assigned to out.

If input a or b change before 10 time units when the result propagates to out, the values of input a and b at the moment of evaluate the outcomes are used and this is known as inertial delay. An input pulse that is shorter than the assignment statement’s delay does not reach the output.

assign #10 out = a & b; // delay in continuous assign

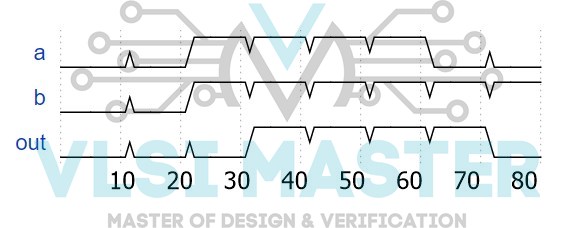

The waveform in Figure 1 is the result executing assign statement. It displays the signal delay.

Fig 1: Waveform

We can observe the following change as when signals a and b become high at time 20, the output signal rises high 10 time units later (time = 30).

And when a falls below 60, the change at 70 falls as well.

Implicit Assignment Delay

A similar way is to express both a delay and a net assignment using an implicit continuous assignment.

//implicit continuous assignment delay wire #5 out = a & b; //same as wire out; assign #5 out = a & b;

The preceding statement is equivalent to specifying a wire out and declaring a continuous assignment on out.

Net declaration Delay

When a delay is stated on a net, it can be defined without placing a continuous assignment on the net.

Any value change made to a net out is postponed if a delay is specified on the net out. In gate-level modelling, net declaration delays can also be employed.

//Net Delays wire #5 out; assign out = a & b; //The above statement has the same effect. wire out; assign #10 out = a & b;

After we’ve gone through continuous assignments and delays, let’s take a deeper look at the expressions, operators, and operands used in continuous assignments.

Inter Assignment Delay

//On the left side, a delay is given. #<delay> <LHS> = <RHS>

An inter-assignment delay statement has a delay value on the assignment operator’s left side.

This means that the statement is performed after the delay has expired, and it is the most frequent type of delay control.

Let us understand with a basic example.

module vd;

reg a, b, c, q;

initial begin

$monitor("[%0t] a=%0b b=%0b c=%0b q=%0b", $time, a, b, c, q);

// Now initialize all signals to 0 at time 0

a <= 0;

b <= 0;

c <= 0;

q <= 0;

// Inter-assignment delay. Wait for #5 time units

// and then assign a and c to 1. Note that 'a' and 'c'

// gets updated at the end of current timestep

#5 a <= 1;

c <= 1;

// Inter-assignment delay. Wait for #5 time units

// and then assign 'q' with whatever value RHS gets

// evaluated to

#5 q <= a & b | c;

#20;

end

endmodule

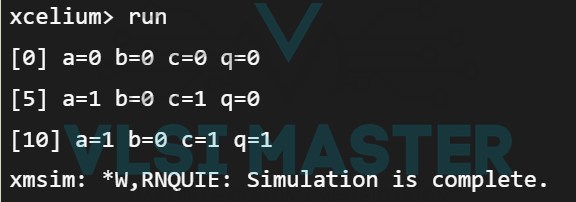

The output of the above example is shown below in figure 2.

Fig 2 Inter Assignment Delay

Intra Assignment Delay

//On the right side, a delay is given. <LHS> = #<delay> <RHS>

An intra assignment delay is one that occurs on the RHS of the assignment operator.

This signifies that the statement has been assessed and that the values of all signals on the RHS have been collected first. It is then allocated to the resulting signal only after the delay has expired.

Let us understand with a basic example.

module vd;

reg a, b, c, q;

initial begin

$monitor("[%0t] a=%0b b=%0b c=%0b q=%0b", $time, a, b, c, q);

// Initialize all signals to 0 at time 0

a <= 0;

b <= 0;

c <= 0;

q <= 0;

// Inter-assignment delay: Wait for #5 time units

// and then assign a and c to 1. Note that 'a' and 'c'

// gets updated at the end of current timestep

#5 a <= 1;

c <= 1;

// Intra-assignment delay: First execute the statement

// then wait for 5 time units and then assign the evaluated

// value to q

q <= #5 a & b | c;

#20;

end

endmodule

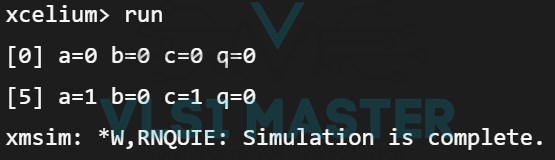

The output of the above example is shown below in figure 3.

Fig 3 Intra Assignment Delay

From this blog, we have learned about the delays for different types of assignment, and in the next blog we will learn about different types of behavioural modeling.

But before studying the next blog, let’s summarise today’s blog in the form of some questions.

- What is dataflow modeling?

- What are the assignment delays?

- What are implicit assignment delays and how do they differ from regular admission delays?

- What do you mean by net declaration delay?

- What is the difference between inter and intra-assembly delays?